# Coplanar Waveguides on Silicon Substrate with Thick Oxidized Porous Silicon (OPS) Layer

Choong-Mo Nam and Young-Se Kwon

**Abstract**— The problem of high dielectric loss of waveguide on silicon in the microwave region can be solved by utilizing a thick silicon dioxide layer that is formed by silicon substrate anodization and oxidation processes. Coplanar waveguides (CPW's) are fabricated on silicon substrate with a 20- $\mu\text{m}$ -thick oxidized porous silicon (OPS) layer and demonstrate very high performance of 0.1-dB/mm attenuation at 4 GHz. Thus, the OPS process is promising for gigahertz applications of silicon substrates.

**Index Terms**— Coplanar waveguide (CPW), oxidized porous silicon (OPS), silicon substrate.

## I. INTRODUCTION

**I**N the microwave region, several types of transmission line such as microstrip line, coplanar waveguide (CPW), and slot line have been utilized [1]–[6]. The use of uniplanar structure, such as CPW, eliminates the need to perform relatively high risk backside thinning, via etch, and plating step. It is especially well suited for use with field-effect transistors (FET's).

Materials such as gallium arsenide, alumina, diamond, and quartz have been the substrates of choice for microwave application because of their low loss. Although silicon has a very mature technology, low cost, and high thermal conductivity, it has not been used as a microwave substrate because of its extremely high dielectric loss.

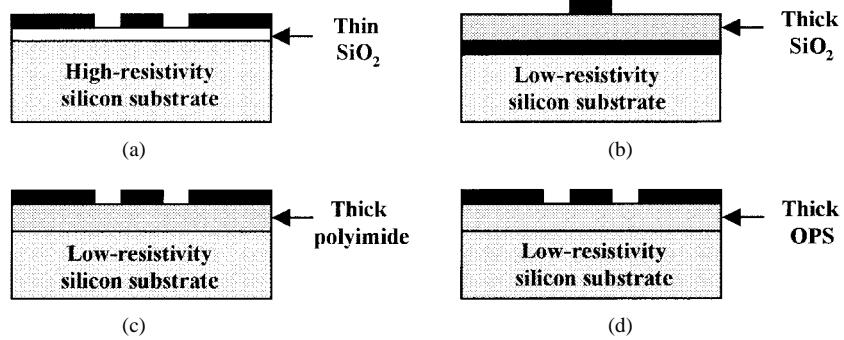

Fig. 1 shows some microwave transmission line structures on silicon substrate. The high-resistivity silicon substrate, shown in Fig. 1(a), is widely used for the microwave region because of its low dielectric loss [1]–[3]. But it is not good for integration of silicon active devices such as MOSFET and BiCMOS. To overcome the problem of high dielectric loss of the low-resistivity silicon substrate, a thick  $\text{SiO}_2$  layer fabricated by chemical vapor deposition (CVD) method [4], shown in Fig. 1(b), and the technology of spin-coated thick polyimide layer [5], shown in Fig. 1(c), are utilized for microwave applications. In the case of a thick  $\text{SiO}_2$  layer fabricated by CVD method, a long process time of  $\text{SiO}_2$  deposition and a high process cost are required. Spin-coated thick polyimide has the advantage of simple process and low cost, but it has the disadvantages, such as water uptake and its lifetime is limited. At this point, the oxidized porous silicon (OPS) layer offers many advantages as a microwave material, including: overcoming high dielectric loss of low-

resistivity silicon substrate in the microwave frequency range; low fabrication cost and time for the thick  $\text{SiO}_2$  layer compare to the CVD method; and negligible water uptake problem in nonhermetic packages.

The problem of high dielectric loss of silicon in microwave region can be solved by utilizing thick silicon dioxide layer which is formed by anodization and oxidation process of silicon substrate. First, the porous silicon layer (PSL) is obtained by anodization process. PSL is oxidized at high temperature with a short oxidation time [7]–[11]. Because the phenomenon of oxidation of porous silicon is due to the reaction of sidewall of trenches, thick oxide layers can be formed very rapidly. These thick oxide layers have been used for the fabrication of integrated circuit [7], [8], optical waveguide [9], microwave package [10], and high-performance microwave planar inductor [11].

In this letter, we fabricated a thick OPS layer on silicon substrate for coplanar waveguide (CPW) with low insertion.

## II. EXPERIMENTAL

The OPS layer was obtained by anodization and oxidation process of silicon substrate. PSL was prepared on (100) boron-doped silicon substrate of 8–10  $\Omega\text{-cm}$  resistivity by an anodization process. The fabrication process of PSL was reported previously [10] and anodic current density was 10 mA/cm<sup>2</sup>. The growth rate of PSL is about 0.46  $\mu\text{m}/\text{min}$  at the anodic current density of 10 mA/cm<sup>2</sup>. The thickness of OPS layer is dependent on PSL thickness, which is determined by anodization conditions such as anodic reaction time and anodic current density. The PSL is preoxidized at 350°C under atmospheric pressure dry oxygen for 30 min. The preoxidized PSL is oxidized for 3 min in wet oxygen at a temperature of 1060°C.

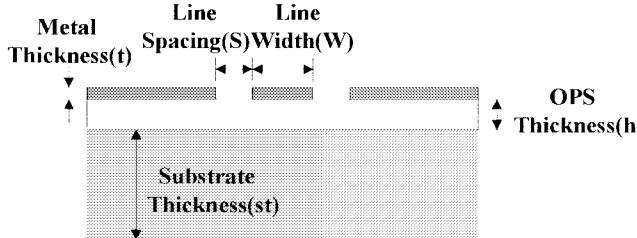

We fabricated CPW on OPS layer with 20- $\mu\text{m}$ -thick  $\text{SiO}_2$  as shown in Fig. 2. The CPW lines consist of two consecutive layers of evaporated Ti/Au followed by 2.5- $\mu\text{m}$  Au plating. The center conductor width ( $W$ ) is 100  $\mu\text{m}$ . But, the gap width ( $S$ ) varies from 20 to 40  $\mu\text{m}$ . The length of transmission lines is 2 mm. To obtain 50- $\Omega$  impedance for CPW on OPS substrate, the  $W$  and  $S$  values are extracted from the Bedair's equation [12]. In Bedair's equation, the value of  $\epsilon_r$  is 3.9.

## III. RESULTS AND DISCUSSION

Manuscript received June 24, 1998.

The authors are with the Department of Electrical Engineering, Korea Advanced Institute of Science and Technology, Taejon 305-701, Korea.

Publisher Item Identifier S 1051-8207(98)09521-X.

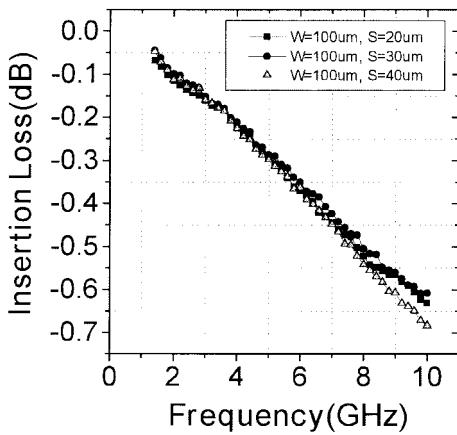

For three different CPW gap widths, the insertion losses were measured as a function of frequency and are shown in Fig. 3. Note that the insertion loss of 2-nm-long CPW's is less

Fig. 1. Structures of microwave transmission lines on silicon substrate. (a) CPW on high-resistivity silicon (HRS) substrate used for low dielectric loss in the microwave frequency range. (b) Microstrip line on thick  $\text{SiO}_2$  layer fabricated by CVD method. (c) CPW on spin-coated thick polyimide layer. (d) CPW on thick OPS fabricated by anodization and short time oxidation process of silicon substrate.

TABLE I

COMPARISON OF DIFFERENT IMPLEMENTATIONS OF TRANSMISSION LINES ON SILICON SUBSTRATE

| Ref.      | Transmission line type | Attenuation (dB/mm @4GHz) | Dielectric material(thickness)      | Metal for signal line(thickness) | Substrate (resistivity)                   |

|-----------|------------------------|---------------------------|-------------------------------------|----------------------------------|-------------------------------------------|

| [1]       | CPW                    | 0.17                      | $\text{SiO}_2$ (0.9 $\mu\text{m}$ ) | Al (1 $\mu\text{m}$ )            | n-type Si ( $\rho=4\Omega\text{-cm}$ )    |

| [4]       | Microstrip             | 0.12                      | $\text{SiO}_2$ (9 $\mu\text{m}$ )   | Au (3.3 $\mu\text{m}$ )          | n-type Si ( $\rho=0.08\Omega\text{-cm}$ ) |

| [5]       | CPW                    | 0.19                      | polyimide (10 $\mu\text{m}$ )       | Al (4 $\mu\text{m}$ )            | p-type Si ( $\rho=20\Omega\text{-cm}$ )   |

| This work | CPW                    | 0.10                      | OPS (20 $\mu\text{m}$ )             | Au (2.5 $\mu\text{m}$ )          | p-type Si ( $\rho=8\Omega\text{-cm}$ )    |

Fig. 2. CPW on thick OPS layer. The microwave passive elements such as high-performance planar inductor, thin film resistor, and MIM capacitor can be fabricated on a thick OPS layer in the microwave frequency range ( $W = 100 \mu\text{m}$ ;  $S = 20, 30, 40 \mu\text{m}$ ;  $t = 2.5 \mu\text{m}$ ;  $h = 20 \mu\text{m}$ ;  $st = 600 \mu\text{m}$ ).

Fig. 3. Insertion loss of CPW on a thick OPS layer as a function of frequency. The insertion loss of CPW ( $W = 100 \mu\text{m}$ ;  $S = 30 \mu\text{m}$ ) of 2-mm length is less than 0.21 dB at 4 GHz.

than 0.21 dB at 4 GHz. Their return losses were measured as a function of frequency and are shown in Fig. 4. Note that

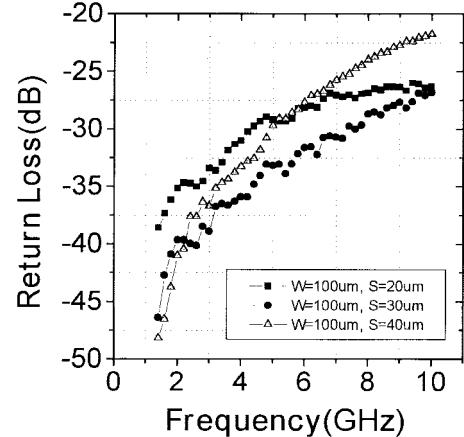

Fig. 4. Return loss of CPW on a thick OPS layer as a function of frequency. The return loss of 2-mm-long CPW's is less than  $-22$  dB at all measured frequency ranges.

the return loss of 2-mm-long CPW's is less than  $-22$  dB at all measured frequency ranges, and very good matching is obtained in case of 30-100-30 ( $S-W-S$ )  $\mu\text{m}$ . These results agree well with the simulation result of Bedair's equation.

Comparison of different transmission lines on silicon substrate is shown in Table I. In the case of thick OPS layer for dielectric material, the lowest attenuation of signal line was obtained.

#### IV. CONCLUSION

Instead of direct oxidation of bulk silicon, a short-time oxidation process of porous silicon can be utilized to make a thick oxide layer for microwave waveguides. CPW's on thick OPS layer demonstrated very high performance, such

as low insertion loss, and the OPS layer is very promising for gigahertz application of silicon substrate.

## REFERENCES

- [1] A. L. Caviglia, R. C. Potter, and L. J. West, "Microwave performance of SOI *n*-MOSFET's and coplanar waveguides," *IEEE Electron Device Lett.*, vol. 12, pp. 26-27, Jan. 1991.

- [2] A. C. Reyes *et al.*, "Silicon as a microwave substrate," in *IEDM Tech. Dig.*, 1995, pp. 1759-1762.

- [3] S. R. Taub, "Temperature dependent performance of coplanar waveguide (CPW) on substrate of various materials," in *IEEE MTT-S Dig.*, 1994, pp. 1049-1051.

- [4] H. Sakai *et al.*, "A new millimeter-wave flip-chip IC on Silicon substrate," in *Asia Pacific Microwave Conf.*, 1994, pp. 291-294.

- [5] B.-K. Kim, B.-K. Ko, and K. Lee, "Monolithic planar inductor and waveguide structures on silicon with performance comparable to those in GaAs MMIC," in *IEDM Tech. Dig.*, 1995, pp. 717-720.

- [6] R. Evans, "Effects of losses on signals in PWB's," *IEEE Trans. Comp., Packag., Manufact. Technol. B*, vol. 17, pp. 217-222, May 1994.

- [7] Y. Watanabe, Y. Arita, T. Yokoyama, and Y. Igarashi, "Formation and properties of porous silicon and its application," *J. Electrochemical Soc.: Solid-State Sci. Technol.*, vol. 122, no. 10, pp. 1351-1355, Oct. 1975.

- [8] K. Imai and S. Nakajima, "Full isolation technology by porous oxidized silicon and its application to LSI's," in *IEDM Tech. Dig.*, 1981, pp. 376-379.

- [9] V.P. Bondarenko *et al.*, "Oxidized porous silicon based waveguide for optical interconnections," in *Proc. 7th Eur. Conf. Int. Opt. (ECIO '95)*, 1995, pp. 291-294.

- [10] C.-M. Nam and Y.-S. Kwon, "SOPS (selective oxidized porous silicon) substrate for microwave power chip-packaging," in *IEEE 5th Topical Meeting Electrical Performance of Electronic Packaging (EPEP '96)*, Oct. 1996, pp. 202-204.

- [11] \_\_\_\_\_, "High performance planar inductor on thick oxidized porous silicon (OPS) substrate," *IEEE Microwave Guided Wave Lett.*, vol. 7, pp. 236-238, Aug. 1997.

- [12] S. S. Bedair and I. Wolff, "Fast, accurate and simple approximate analytic formulas for calculating the parameters of supported coplanar waveguides for (M)MIC's," *IEEE Trans. Microwave Theory Tech.*, vol. 40, pp. 41-48, Jan. 1994.